«Энцелад» – это не «Эльбрус» и не Байкал»

10 Янв 2022

Микроэлектронный дизайн-центр Malt System, созданный десять лет

назад при МГУ, разработал и зарегистрировал в Роспатенте процессор

с собственной архитектурой для потоковой обработки сетевого трафика.

Российская команда разработчиков многоядерных процессоров,

компания Malt System прошла процедуру регистрации топологии своего

нового процессора, получив свидетельство Роспатента.

В модельном ряду компании новинка имеет наименование Malt-Cv3,

коммерческое ее название – «Энцелад» (имя одного из титанов

в древнегреческой мифологии, перекочевавшее к шестому по размеру

спутнику Сатурна).

По данным разработчиков, «Энцелад» предназначен для потоковой

обработки сетевого трафика на скорости до 1 Гбит/с, в том числе

обеспечения безопасности сетевых соединений «путем программного

шифрования/дешифрования трафика по любым отечественным или

зарубежным алгоритмам».

В компании чип называют третьим в линейке процессоров Malt-C,

предназначенных для выполнения сложных криптопреобразований, и первым

«встраиваемым и исключительно компактным». Последнее обстоятельство

объясняется тем, что он будет иметь размеры не более 9×9 мм в корпусе типа

BGA (англ. Ball Grid Array, массив шариков). «Это меньше, чем разъем RJ-

45, – отмечают разработчики. – Такой процессор действительно можно

встроить практически в любое устройство».

«Энцелад» спроектирован по технологии 16 нм. Его создание Malt

System анонсировала в середине мая 2020 г. О размещении заказа на выпуск

чипов на контрактной тайваньской фабрике TSMC компания сообщила 30

июля 2021 года. Получить образцы «в кремнии» разработчики надеются

в I квартале 2022 года. Выпуск SDK и отладочной платы для «Энцелада»

запланирован на III квартал 2022 года.

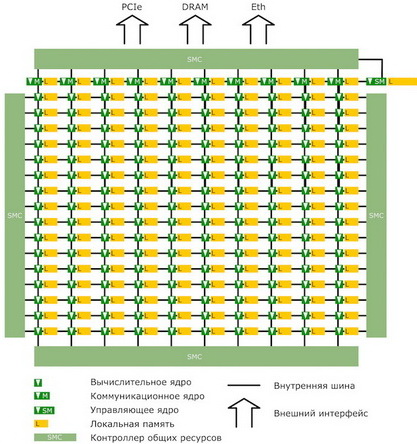

В компании отмечают, что «Энцелад» построен на ее собственной

оригинальной архитектуре Malt. Ее основу составляют десятки или сотни,

в зависимости от модели, компактных асинхронных универсальных

вычислительных ядер, объединенных одной или несколькими

оригинальными сетями worm-hole с топологией типа fat-tree, описывают

свою архитектуру разработчики.

«Коммуникация между сетями — программно-аппаратная, – сообщают

они. – Иерархия универсальных ядер включает три уровня: supermaster –

управляющее ядро, master – коммуникационные ядра, slave – доступные для

задач пользователя вычислительные ядра. Slave-ядра могут содержать

векторные ускорители, выполняющие специализированные задачи целевого

класса, каждый ускоритель содержит от восьми до 128 однотипных

процессорных элементов с общей памятью команд. Все вычислительные ядра

и ускорители имеют собственную локальную память данных. Все

универсальные ядра непосредственно адресуют общую внешнюю

динамическую память DRAM и другие общие ресурсы (PCIe, Ethernet,

SATA)».

Непосредственно в «Энцеладе» организовано четыре вычислительных

кластера, каждый из которых содержит 16 специализированных ядер

и находится под управлением одного универсального RISC-ядра.

На кристалле размещены два контроллера 1GEb Ethernet, семь процессорных

RISC-ядер общего назначения, три блока SIMD-ускорителей, блок общей

статической памяти, контроллеры SPI-Flash, UART, GPIO.

Взаимодействие c процессором осуществляется через универсальные

интерфейсы SPI, UART, GPIO, которые также контролируется одним

выделенным универсальным ядром. На чипе будет доступно 512 кБ общей

статической памяти SRAM, а также планируется поддержка до 64

МБ внешней памяти типа HyperRAM/HyperFLASH.

Расчетная рабочая частота процессора составит 1,2 ГГц. В чипе

реализован IP-блок генератора частот с автоматической подстройкой без

импульсных помех FDPLL. Прогнозируемое энергопотребление новинки

на полной нагрузке не должно превысить 3 Вт. В типовых режимах,

в зависимости от реализованного алгоритма, энергопотребление должно

оказаться в пределах 500-2000 мВт.

По материалам СМИ

Список Новостей